Hi There,

I'm Parv Rasadiya

i am

i am

I am a dedicated VLSI engineer currently pursuing M.Tech at PDEU, with hands-on experience in FPGA development, IC layout design, and digital verification. I've gained valuable exposure through internships at SVNIT and Rhino Machines, and I'm actively involved in teaching as a Teaching Assistant. My interests lie in RTL design, physical design, and ASIC workflows. I enjoy solving real-world problems and bringing innovative ideas from concept to silicon.

phone : +91 63553 40719

email : work.parvrasadiya@gmail.com

place : Surat, Gujarat, India

Industry-standard EDA platforms, semiconductor ecosystems & hardware tools I work with

Education is not the learning of facts, but the training of the mind to think !

M.Tech in VLSI Design | CGPA : 9.5/10

B.Tech in Electronics Engineering

HSC Science | GSEB

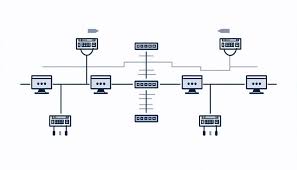

Designed and verified SPI and UART modules using Verilog. Verified using simulation and testbenches for serial communication integrity.

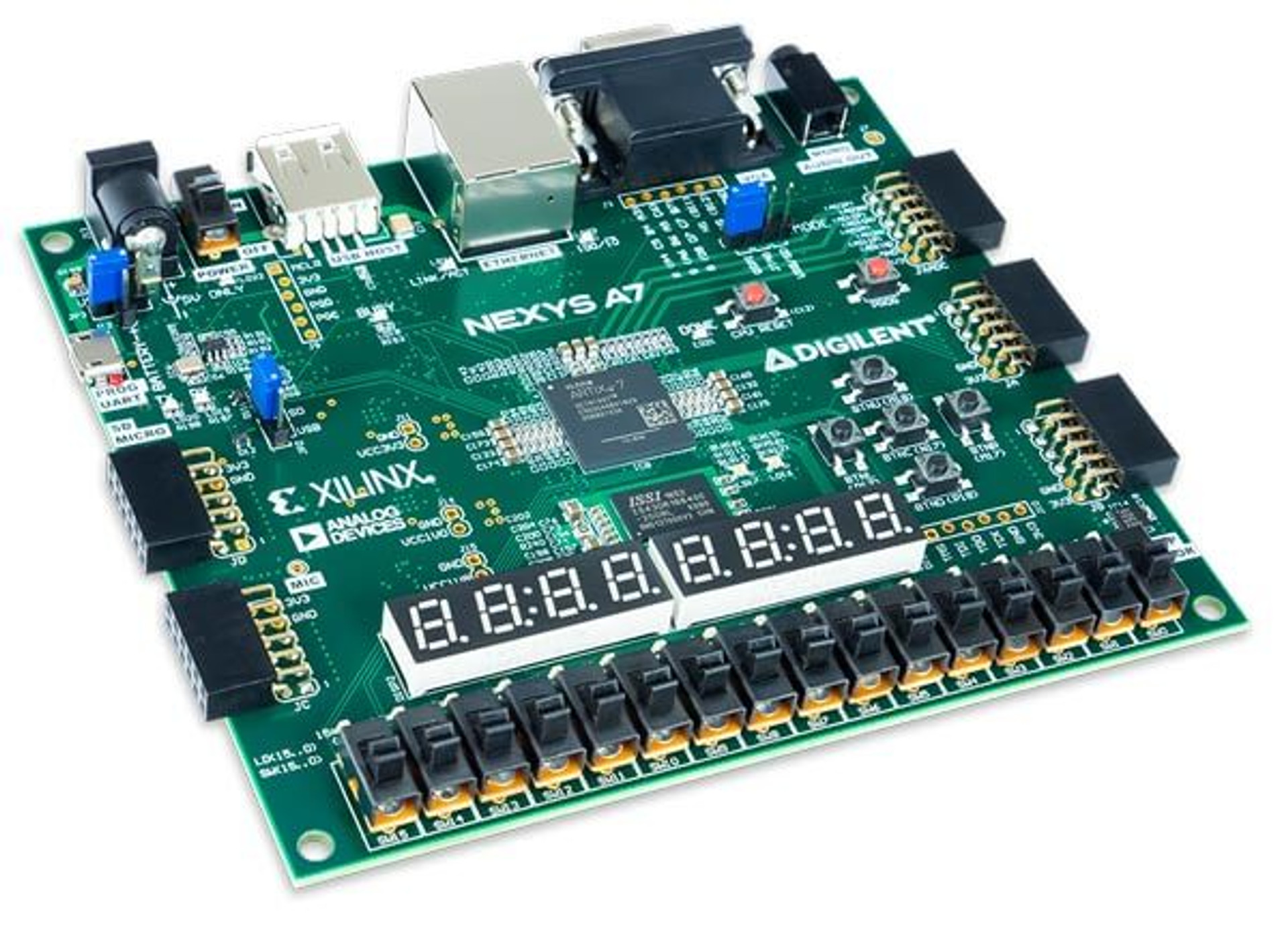

Used Verilog to compute and display the sum of N natural numbers on a 3-digit 7-segment display using FSM and Double Dabble algorithm. Implemented on Artix-7 using Xilinx Vivado.

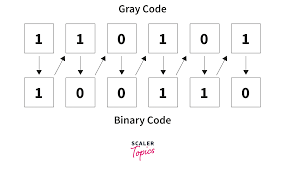

Designed a compact XOR gate using 4 transistors in Cadence Virtuoso and implemented a Binary to Gray code converter using it. Complete layout designed and tested.

An IoT-based parking system is a centralized management that enables drivers to search for and reserve a parking spot remotely through their smartphones.

4x4x4 LED Cube has 64 LEDs. These are all wired to a Arduino Uno. An Arduino is a single-board microcontroller, a 3D LED cube can be used for displaying various patterns or structures in 3 dimensional plane.

Completed a 5-week hands-on training in VLSI design, semiconductor fabrication, cleanroom processes, and IC packaging techniques.

Assisting professors in lecture preparation, grading, and mentoring students in VLSI and digital design subjects.

Led the publicity team for UDAAN'24, BVM's 3-day techno-cultural fest. Managed promotions, coordinated volunteers, and drove student engagement.

Worked on a PLC-based industrial weighing system. Integrated hardware into automation systems and collaborated with the automation team.

Contributed to PCB design, component footprint verification, soldering, and R&D testing of hardware modules in the electronics lab.

“Each certificate is not just paper — it’s proof of passion, persistence, and purpose.”

Advanced Verification and UVM

SystemVerilog for Design and Verification v21.10

Verilog Language and Application v28.0

RTL to GDSII using Synopsys EDA Tools

5-Week Training Program – Suchi Semicon @ SVNIT

Cadence RTL to GDSII Flow v6.0

Fundamentals of VLSI

OCI Generative AI Professional

TCS iON Career Edge - Young Professional